Getting started with IPKISS Link for Siemens EDA¶

Installing a license file¶

Make sure both the Tanner L-Edit and IPKISS licenses are working. Please refer to License types for full instructions on how to setup the licensing.

Note

OpenAccess databases

If this is your first time you use an OpenAccess (OA) enabled electronic design automation (EDA) tool, here is some terminology that you should be aware of:

- OpenAccess (OA)

A standard interface for software tools to use IC design databases. OpenAccess is an application programming interface (API) to databases which hold design information, such as for electronic or photonic ICs. For instance, an OA database can contain technology settings, and different cells with layout data and schematic data, up to complete IC designs. OA allows different software tools to access such database through a standard. The demonstration libraries in this tutorial are OA libraries, generated by IPKISS, using the standard OA database implementation. You can see it as a collection of files representing technology and design information.

- lib.defs

A file that describes the the name and location of each library included in an IC design project, supported by the major tools.

- OpenAccess attached library

A library that is used as technology reference. The technology settings (layers, grid, database units) are loaded from this library. It may also contain a series of predefined components (grating couplers, waveguides, couplers, splitters, ring resonators, …).

Using the example library¶

A demonstration library and associated projects are included in the samples folder of your installation

(typically under %USERPROFILE%\luceda\samples\ipkiss390). The organization of this library is explained in Library organization.

Here, we just demonstrate how the library can be opened.

Starting L-Edit¶

The L-Edit / IPKISS integration will be loaded as soon as you open a library made with IPKISS. Therefore, you can just double-click on L-Edit in the start menu and open a library, or you can double-click on the lib.defs file of said library.

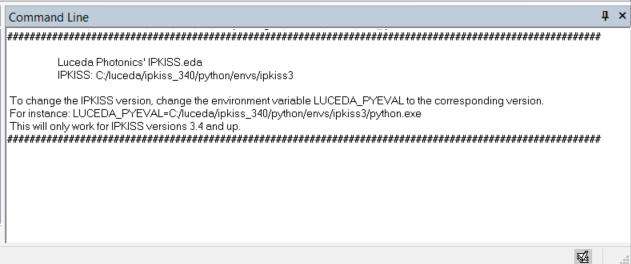

You can check if the integration is loaded by looking for the following message in the L-Edit console window.

The L-edit / IPKISS integration message.¶

Note

The IPKISS version used in the integration is set using the environment variable LUCEDA_PYEVAL. This is normally set during the installation.

To set or change the IPKISS version, change the environment variable to a different python executable. For instance:

LUCEDA_PYEVAL=C:/luceda/ipkiss_340/python/envs/ipkiss3/python.exe

This will only work for IPKISS versions 3.4 and up.

Loading the demonstration project¶

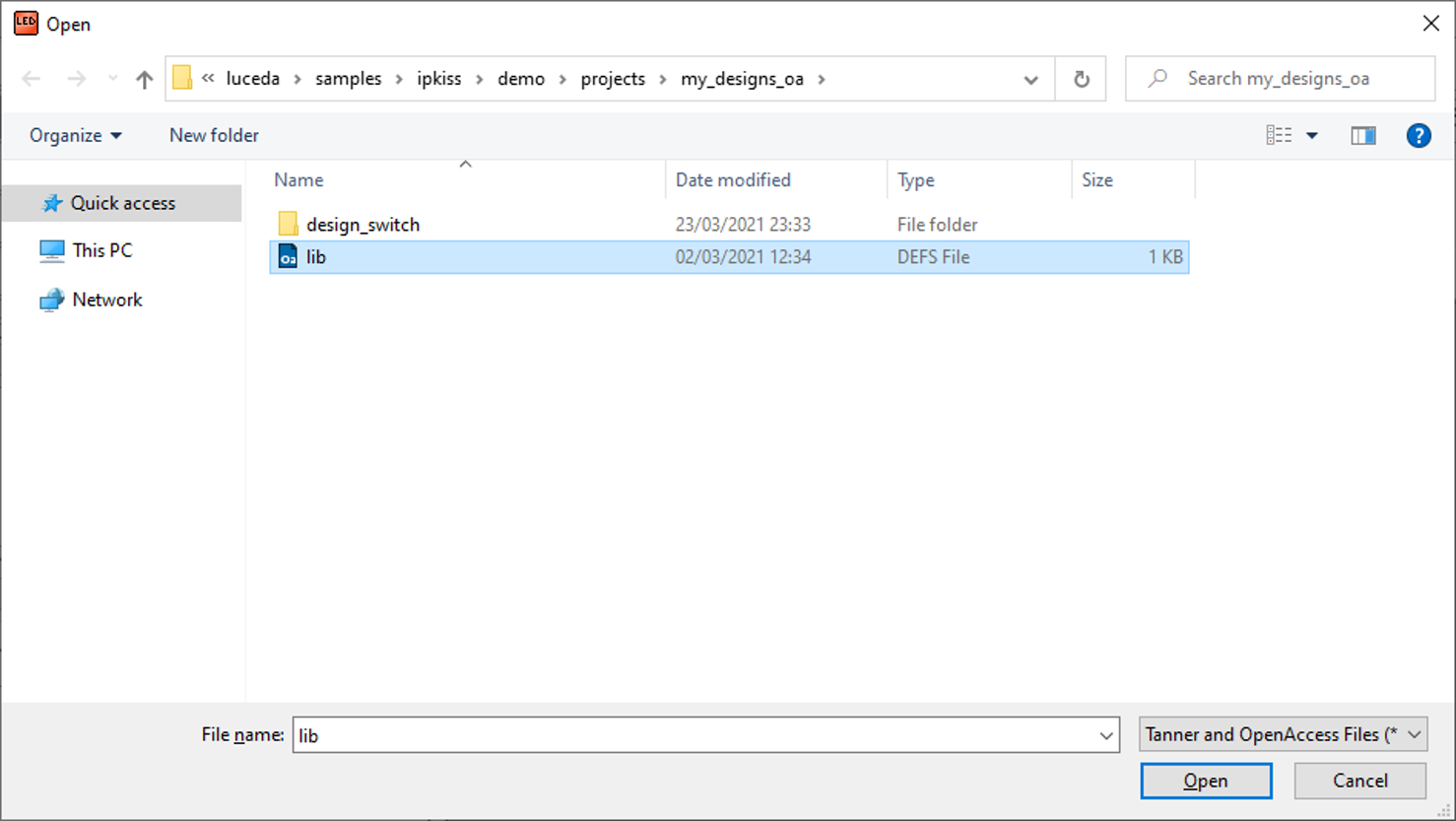

To load the demo project, we use File –> Open, and open the lib.defs project file from \demo\projects\my_designs_oa under the %USERPROFILE%\luceda\samples\ipkiss390 directory.

Open the demonstration project in L-Edit.¶

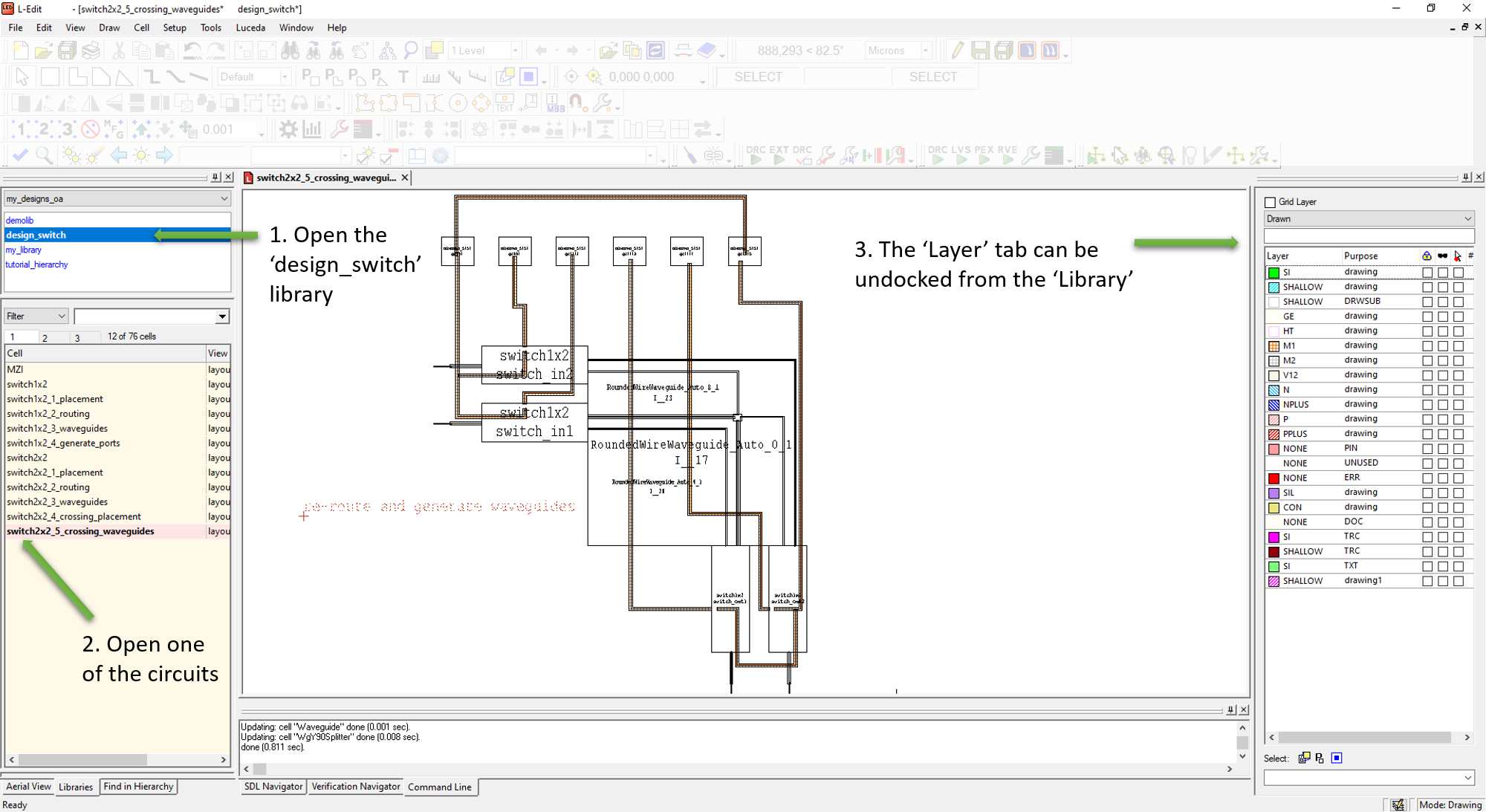

Select design_switch as the top-level library, and open one of the circuit examples.

The demonstration project contains several libraries: the PDK (demolib), custom components (my_library), example design (design_switch) and a tutorial (see next chapter).¶

Note

IPKISS Link for Siemens EDA requires that the user’s main design is saved to an OA database. All libraries or PDKs exported by IPKISS Link for Siemens EDA’s pdktools are also OA databases. Cells from Tanner Database Files (.tdb) can still be instantiated.